# **ReadGuard: Integrated SSD Management for Priority-Aware Read Performance Differentiation**

MYOUNGJUN CHUN, Seoul National University, Seoul, Korea (the Republic of) MYUNGSUK KIM, Kyungpook National University, Daegu, Korea (the Republic of) DUSOL LEE, Seoul National University, Seoul, Korea (the Republic of) JISUNG PARK, POSTECH, Pohang, Korea (the Republic of) JIHONG KIM, Seoul National University, Seoul, Korea (the Republic of)

When multiple apps with different I/O priorities share a high-performance SSD, it is important to differentiate the I/O QoS level based on the I/O priority of each app. In this paper, we study how a modern flash-based SSD should be designed to support priority-aware read performance differentiation. From an in-depth evaluation study using 3D TLC SSDs, we observed that existing FTLs have several weaknesses that need to be improved for better read performance differentiation. In order to overcome the existing FTL weaknesses, we propose ReadGuard, a novel priority-aware SSD management technique that enables an FTL to manage its blocks in a fully read-latency-aware fashion. ReadGuard leverages a new read-latency-centric block quality marker that can accurately distinguish the read latency of a block and ensures that higher-quality blocks are used for higher-priority apps. ReadGuard extends an existing suspend/resume technique to handle collisions among reads. Our experimental results show that a ReadGuard-enabled SSD is effective in supporting differentiated read performance in modern 3D flash SSDs.

CCS Concepts: • Hardware → External storage; • Information systems → Flash memory; Storage management.

Additional Key Words and Phrases: SSD, flash memory, read latency optimization, I/O priority

# 1 Introduction

Modern solid-state drives (SSDs) play a crucial role in serving apps that directly interact with users in large-scale data centers. Such latency-sensitive apps (e.g., web services [1], online transaction processing [2], and AI/ML inference apps [3, 4]) are commonly required to satisfy strict service-level agreements (SLAs). For instance, an online transaction processing app should process user requests and return responses with sub-second latency [5]. To meet SLA requirements, an ideal approach might be to develop a dedicated storage system for each app so that there is no interference among different apps. However, this approach is impractical for data centers due to its low cost-performance ratio, inefficient energy use, and extensive space needs [6, 7]. As a practical alternative, a data center employs shared storage systems that are shared among latency-sensitive apps as well as throughput-oriented apps (e.g., graph processing, data analysis, and backup tasks) that are less sensitive to I/O latency.

When a latency-sensitive app and a throughput-oriented app run concurrently in a storage system, we would desire the I/O latency of the latency-sensitive app to be shorter than that of the throughput-oriented app. To serve latency-sensitive apps with shorter I/O latencies in a shared storage system, several studies [8–14] have proposed

Authors' Contact Information: Myoungjun Chun, Seoul National University, Seoul, Korea (the Republic of); e-mail: mjchun@davinci.snu.ac.kr; Myungsuk Kim, Kyungpook National University, Daegu, Korea (the Republic of); e-mail: ms.kim@knu.ac.kr; Dusol Lee, Seoul National University, Seoul, Korea (the Republic of); e-mail: dslee@davinci.snu.ac.kr; Jisung Park, POSTECH, Pohang, Korea (the Republic of); e-mail: jisungpark@postech.ac.kr; Jihong Kim, Seoul National University, Seoul, Korea (the Republic of); e-mail: jihong@davinci.snu.ac.kr.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. Copyrights for third-party components of this work must be honored. For all other uses, contact the owner/author(s). © 2024 Copyright held by the owner/author(s).

ACM 1553-3093/2024/7-ART

https://doi.org/10.1145/3676884

solutions that differentiate I/O latencies among multiple apps based on their priorities. FlashShare [8], for example, successfully reduced the average and p99-percentile read latency of a latency-sensitive app by enhancing the kernel-level I/O stack based on I/O priority. To address SSD-level read latency, which can constitute up to 91% of total I/O latency in a modern I/O stack with an NVMe interface [15], some works [11–14] have proposed SSD-level scheduling techniques that reorder read requests based on their I/O priority within device-level queues. In this paper, we argue that (1) existing priority-aware I/O management techniques at various I/O stack layers are not sufficient to differentiate SSD-level latencies among different apps in modern 3D flash SSDs, and (2) the I/O priority of an app should be carefully managed inside an SSD from the NAND block level to main FTL modules for priority-aware I/O performance differentiation. Since read latency is a crucial factor in determining the perceived I/O performance for the majority of applications, this paper focuses on differentiating read latency.

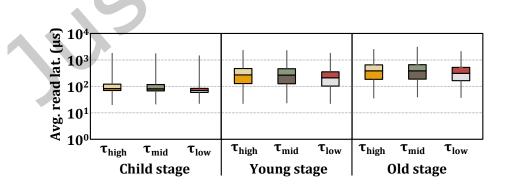

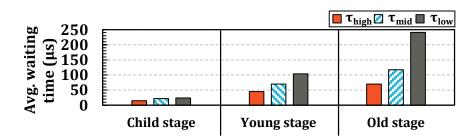

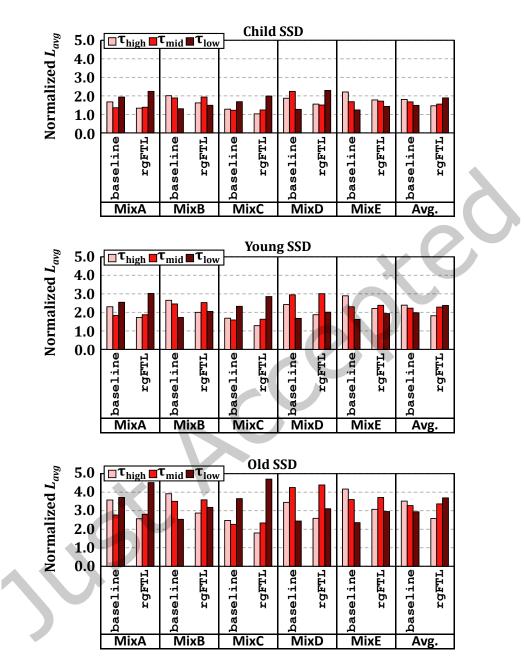

To understand how well a modern 3D flash SSD supports the read-latency differentiation requirement, we evaluated the read-latency (at the SSD level) distributions of apps using an NVMe SSD simulator with three priority I/O queues. Our simulation environment supports an SSD-level priority-aware scheduling mechanism proposed by previous studies [11–14] (see Section 2.4 for more details on the priority-aware FTL). Figure 1 shows the read-latency distributions of three apps,  $\tau_{high}$ ,  $\tau_{mid}$ , and  $\tau_{low}$ , where the I/O priority of  $\tau_{high}$  is the highest while that of  $\tau_{low}$  is the lowest.<sup>1</sup> Note that the read latency of Figure 1 represents the end-to-end read latency of an SSD from the time an app enqueues a read request to a submission queue to the time when the read response arrives at the host. As shown in Figure 1, the SSD did not adequately support read differentiation. In all three stages of the SSD lifetime, the average read latency of three apps was virtually indistinguishable regardless of the I/O priority of an app.

To identify the root causes of poor read differentiation over app priorities in our priority-aware SSD, we performed a comprehensive study from a NAND flash memory to an FTL and identified three main causes of poor read differentiation. First, the key modules of existing priority-aware FTLs (such as [11–14]) work in a read-latency-unaware fashion. For example, these FTLs assume that the read latency of flash blocks in an SSD is equal. Therefore, when the read latency of flash blocks is significantly different (as observed in modern 3D flash blocks), the existing priority-aware FTLs cannot properly support I/O requests with different priorities. For example, in our benchmark evaluations, we observed frequent block-quality inversions among apps, allocating blocks with shorter read latency to lower-priority apps. Second, conventional block quality measures (e.g., program/erase (P/E) cycles) are inadequate to differentiate the read latency of modern 3D flash blocks with high process variability. Since a large variation in the read latency of 3D flash blocks is directly related to the number

<sup>1</sup>See Section 3.2 for more details on the evaluated apps and SSD lifetime stages.

Fig. 1. Read-latency distributions among three apps.

of read-retry operations, a better block quality measure, which focuses on the read latency of flash blocks, is needed so that the number of read-retry operations of a block can be accurately predicted. Third, the existing priority-aware FTLs do not properly handle the conflict between two NAND read commands with different priorities. Existing command schedulers preempt only ongoing writes and erases over reads, without considering the case when a lower-priority read conflicts with a higher-priority read, which can cause a large delay for the higher-priority read when the lower-priority read requires a long latency to complete.

Motivated by our findings from the evaluation study, we propose a new integrated *priority-aware* flash management scheme, ReadGuard, which can better differentiate read latency between apps with different priority requirements. ReadGuard makes three key contributions. First, we propose a novel read-latency-centric block quality marker that can accurately represent the (worst-case) read latency *tREAD* of each block. By estimating the read latency of a block, not the reliability of data stored in the block (as in common block quality measures such as P/E cycles), the proposed block quality marker enables read-latency-aware block management in ReadGuard. Second, ReadGuard adopts a priority-aware block management scheme based on the proposed block quality marker. A ReadGuard-based FTL allocates blocks with short read latency to a higher-priority app and continuously monitors the quality level of the allocated blocks so that high-priority read requests can be serviced from the high-quality blocks. Third, we propose a priority-aware fashion, a higher-priority read should be able to preempt an ongoing lower-priority read command. Otherwise, a higher-priority read command will experience an excessive amount of delay because a lower-priority read tends to be serviced from a block with long read latency.

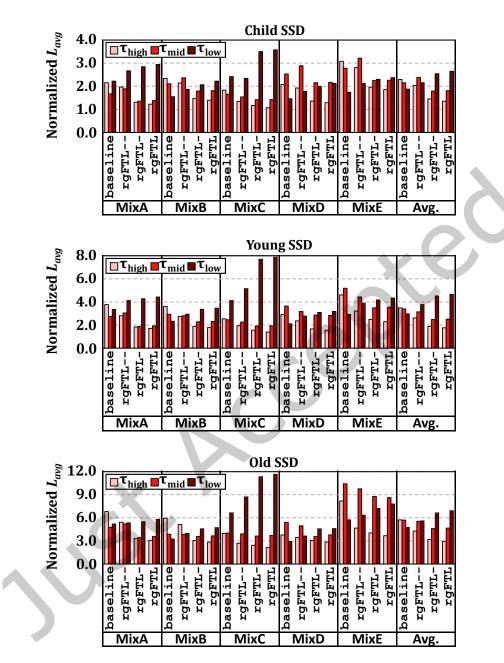

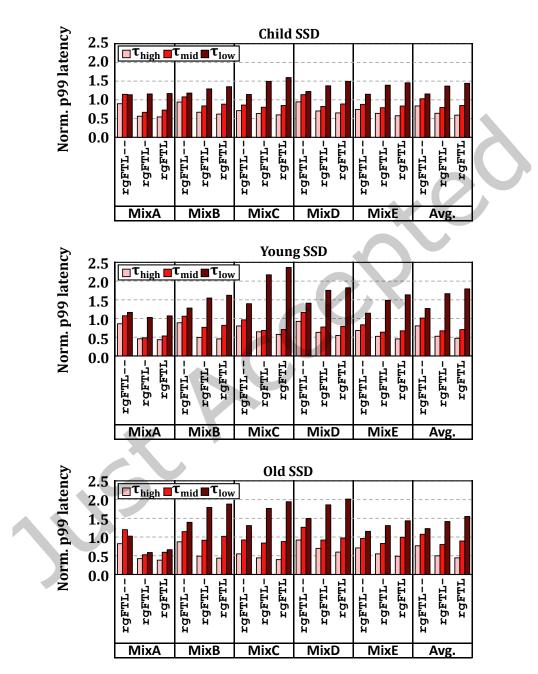

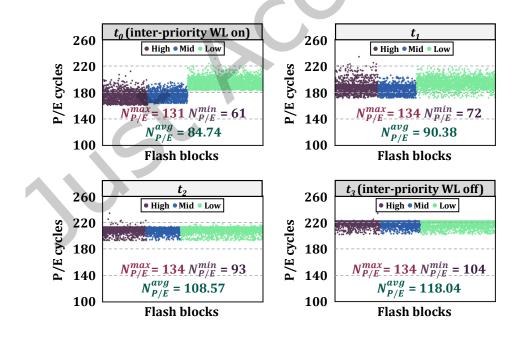

In order to evaluate the effectiveness of ReadGuard, we have implemented a ReadGuard-enabled FTL, rgFTL, using an open SSD simulation platform [11]. Our experimental results using various real-world workloads show that rgFTL can effectively differentiate the read performance of apps according to their I/O priorities. In rgFTL, the average read latency of the highest-priority app is up to 57.1% shorter than that of the lowest-priority app while the baseline FTL does not differentiate the read latency between these apps. Furthermore, rgFTL reduces the 99th-percentile read tail latency of high-priority apps by up to 55.5%. Although rgFTL needs additional block copy operations to avoid block-quality inversions among apps, their impact on SSD lifetime and performance is not significant. RgFTL increases the average write latency by by about 2.8% because additional page writes, which are needed to avoid block-quality inversions among apps, incur additional garbage collection.

# 2 Background

In order to support priority-aware read differentiation, our proposed technique requires understanding key parameters of NAND flash memory that affect the flash read latency. Therefore, we review the basics of the flash read latency and the impact of read errors on the flash read latency. We also briefly present an overview of an existing priority-aware SSD.

# 2.1 NAND Flash Memory Basics

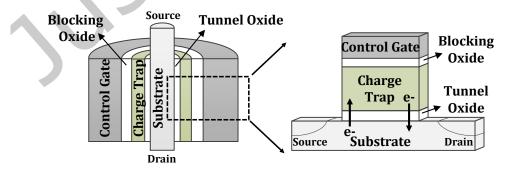

A flash cell is the fundamental component of NAND flash memory. Figure 2 depicts its organization, with components such as the charge trap, blocking oxide, control gate, and tunnel oxide. Controlling the number of electrons in a flash cell's charge trap allows data to be stored. The threshold voltage ( $V_{th}$ ) level of the flash cell distinguishes the binary data stored in it, which is either '0' or '1'. To change the  $V_{th}$  of the flash cell, electrons are either injected into or removed from the charge trap. This electron movement is facilitated by the tunnel oxide, a thin layer of insulating material between the substrate and the charge trap.

In a flash die, individual flash cells are organized into a hierarchical structure. Each flash die has several planes and hundreds to thousands of blocks within each plane. Each of these blocks is composed of multiple sub-blocks.

The sub-blocks are represented as matrices with rows and columns composed of flash cells. These horizontal rows, known as wordlines (WLs), connect the flash cells' control gates, whereas the vertical columns, known as bitlines (BLs), connect the cells' drain and source terminals. When a wordline (WL) is activated, the same voltage is applied to all cells of the target WL, allowing for simultaneous read and write operations across all cells on the WL. The type of NAND flash decides how many pages a single WL corresponds to. For example, in a triple-level cell (TLC) NAND flash memory, each WL is associated with three pages (MSB, CSB, LSB pages).

A read, a program, and an erase operation are the three fundamental operations of NAND flash memory. A *read* operation applies a specific voltage, read reference voltage  $V_{ref}$ , to distinguish between  $V_{th}$  levels of flash cells in target WL. The Flash chip determines the stored data by observing whether the current flows or not through the BLs. A *program* operation applies a high voltage (e.g., 20V) to the cell's control gate through its target WL. As a result of the voltage difference, electrons from the substrate tunnel through the gate oxide and are trapped in the charge trap, thus increasing the  $V_{th}$  level of the cell. An *erase* operation operates at the block granularity, whereas read and program operations operate at the page granularity. To erase the data within the target block, the flash chip applies a high voltage (e.g., 20V) to the source terminal. The voltage difference causes electrons to tunnel from the charge trap to the substrate via the tunnel oxide so that the  $V_{th}$  levels of all cells in the block are returned to the initial states.

## 2.2 Read Errors in NAND Flash Memory

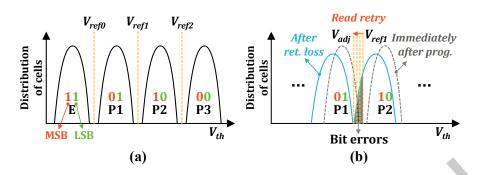

Despite its nonvolatile nature, NAND flash memory is inherently prone to errors. Various error sources, such as retention loss [16, 17] and program disturb [18], can shift the  $V_{th}$  levels of flash cells beyond the  $V_{ref}$  value, leading to potential bit errors in NAND flash memory. Figure 3 shows the  $V_{th}$  distribution in a WL of MLC NAND flash memory, that employs four distinct  $V_{th}$  levels to store two bits per cell (E, P1, P2, and P3). Reference voltages ( $V_{ref0}, V_{ref1}, \text{and } V_{ref2}$ ) are used to determine the  $V_{th}$  levels of flash cells. The  $V_{ref1}$  reference voltage distinguishes P(i - 1) and P(i). In the initial state, as shown in Figure 3(a), all  $V_{th}$  levels can be reliably distinguished using reference voltages. Retention loss, however, causes unintended shifts in the  $V_{th}$  levels, making it more likely to overlap with  $V_{ref1}$ . The stored bits in the overlapped region of flash cells flip, resulting in raw bit errors of read data.

The number of bit errors in read data is directly affected by the error characteristics of the target flash cells. The high voltage stress involved in repetitive program/erase operations (i.e., P/E cycles) accelerates the deterioration of a flash cell's tunnel oxide. This deterioration weakens its insulating capabilities, resulting in rapid charge leakage from the charge trap into the substrate. Furthermore, due to manufacturing process variations, particularly in 3D NAND flash memory, the initial thickness of the tunnel oxide may differ between flash cells [19–21]. Flash cells

Fig. 2. An organization of a flash cell.

ReadGuard: Integrated SSD Management for Priority-Aware Read Performance Differentiation . 5

Fig. 3. Changes in  $V_{th}$  distribution of MLC flash cells and  $V_{ref}$  adjustment in a read-retry operation.

with a thinner oxide layer are inherently more susceptible to sustained voltage stress, causing them to wear out faster. As a result, even when two WLs are exposed to the same error sources, the number of bit errors in their stored data can vary significantly depending on their P/E cycles and inherent error characteristics.

# 2.3 Read-Retry in Modern SSDs and Its Impact on Read Latency

To ensure data reliability despite the heterogeneous error characteristics of modern NAND flash memory, modern SSDs use strong error-correcting codes (ECC) that can correct several tens of raw bit errors. Unfortunately, due to the high raw bit-error rate (RBER), even such a strong ECC often fails to correct all bit errors in modern NAND flash memory. To address this, when the RBER of a read page exceeds the ECC correction capability (i.e., the number of correctable bit errors), a modern SSD performs an *read-retry* operation. The read-retry operation repeats reading of the page with adjusted  $V_{ref}$  values until the page's RBER falls below the ECC capability or until a set number of retry attempts is reached [19, 20, 22–25]. Although read-retry is highly effective at ensuring data reliability, it significantly increases the effective read latency of NAND flash memory, almost linearly with the number of retry steps. Three read voltage adjustments are needed to retrieve the correct data (with  $V_{adj}$ ) in Figure 3(b), for instance, resulting in four times the normal read latency.

In general, the device-level latency tREAD for reading a flash page can be expressed as  $tREAD = (tR + tDMA + tECC) \times (N_{retry} + 1)$  where tR is the flash page access time, tDMA is the data transfer time from a flash chip to a flash controller, and tECC is the error correction time by the ECC engine. While tR, tDMA, and tECC are fixed by flash manufacturers (i.e., they do not change during run time),  $N_{retry}$  significantly varies depending on the number of errors on the target page.

## 2.4 Overview of a Priority-Aware SSD

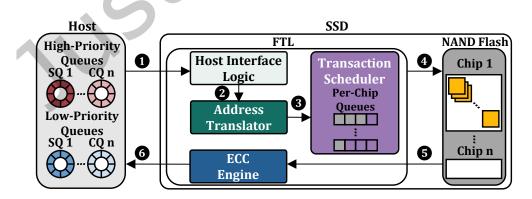

Although the flash read latency *tREAD* is a key parameter in deciding the read latency at the app level, the host-side read latency is significantly affected as well by SSD-internal states at the time of the read request issue. Figure 4 illustrates how a read request *r* is processed in a priority-aware SSD [11–14]. When the host issues *r* containing a target logical block address (LBA) range, an address of host-side read buffer, and its priority, it is first transferred to the host interface logic in the SSD (**①**). The host interface logic splits the LBAs in the target request range into a series of *m* flash read requests (i.e., *m* transactions) (**②**). An LBA address of each flash read request is converted to a physical page address (PPA) by the address translator. A transaction with a PPA (i.e., a read command to the PPA) is then enqueued into a per-chip queue that is responsible for serving the PPA (**③**). The transaction scheduler decides which transaction is issued first by prioritizing the pending transactions in per-chip queues. When the status of the target flash chip is ready, the highest priority request is issued to the

flash chip ( $\P$ ). An ECC engine corrects potential error bits of the requested page ( $\P$ ) before the page is sent to the host-side completion queue ( $\P$ ).

In existing priority-aware SSDs, regardless of a request priority, read commands are handled first over other flash commands (i.e., write and erase commands). When a read command is selected by the transaction scheduler, if a program command or an erase command is currently serviced at the same target flash chip, the transaction scheduler preempts the ongoing program/erase command by suspending its operation so that the read command can be serviced first [26, 27]. That is, read/write and read/erase interferences are minimized by command suspension techniques in the existing prior-aware SSDs. However, if the ongoing command is read, existing transaction schedulers [28] do not suspend the ongoing read command even if its priority is lower than that of the newly selected read command.

When a host read request r requires m flash reads to m LBAs,  $a_r^0, ..., a_r^{m-1}$ , the host-side read latency L(r) is given by  $max\{l(a_r^0), ..., la_r^{m-1}\}$  where l(a) represents the read latency of a read request to the LBA a that measures from when a read request to the LBA a is fetched by an FTL to when the read request is completed. The read latency l(a) of a read request to the LBA a consists of two terms, the flash-device latency for reading from the LBA a and the waiting time before a flash read command is issued for accessing the LBA a.

## 3 Root Cause Analysis

In this section, we explain key reasons for poor read differentiation in existing priority-aware SSDs. In a priorityaware SSD, if the I/O priority of  $r_i$  is higher than that of  $r_j$ , the transactions for  $r_i$  have a higher priority over those for  $r_j$ . Therefore, the transactions for a higher-priority request experience shorter waiting times over those for a lower-priority request, thus effectively supporting the waiting time differentiation over I/O priorities. For example, Figure 5 shows the average waiting time of the same three apps in Figure 1. Unlike the read-latency distributions (shown in Figure 1), the waiting times are quite nicely differentiated according to the I/O priority of the apps. Furthermore, since an incoming read command can preempt ongoing program/erase operations for serving the incoming read first, other flash operations do not interfere with read operations. Therefore, we start from the device level read latency *tREAD* to investigate the root causes of poor read differentiation.

# 3.1 Cause 1: Large Variations in Read Latency

Modern SSDs suffer from a large number of  $N_{retry}$  from the capacity-centric cell design (e.g., TLC and QLC) that makes SSDs to be more vulnerable to quick  $V_{th}$  shifts beyond  $V_{refi}$  after programmed [20, 21, 24]. Furthermore, the manufacturing process of modern flash chips introduces substantial process variability in terms of reliability

Fig. 4. Key steps of read request processing.

ReadGuard: Integrated SSD Management for Priority-Aware Read Performance Differentiation • 7

Fig. 5. Comparisons of average waiting times of three apps.

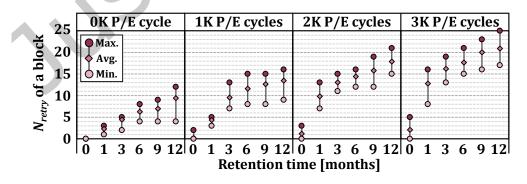

between flash blocks [21]. To understand how these trends affected the variation in read-latency distribution in an SSD, we performed comprehensive evaluations using 160 real 3D TLC flash chips. We measured the block-level read latency (i.e.,  $N_{retry}$  of the worst page of a block) of more than 10,000 blocks under different P/E cycles and retention times. (When no confusion arises,  $N_{retry}$  of a block is used to mean  $N_{retry}$  of the worst page in a block.)

Figure 6 shows block-level  $N_{retry}$  distributions for the tested blocks under different operating conditions. We make two key observations from Figure 6. First, there are substantial block-level  $N_{retry}$  variations among flash blocks. For example,  $N_{retry}$  value of a block can vary significantly from 0 to 25. Such a large variation on  $N_{retry}$  between blocks can be attributed to inter-block process variability of a 3D flash manufacturing process as well as different operating conditions (e.g., P/E cycles or retention times). Therefore, when flash blocks experience different P/E cycles and retention times, they exhibit different levels of raw bit errors, thus resulting in significant variations of  $N_{retry}$ .

Furthermore, even under the same P/E cycle and retention time condition,  $N_{retry}$  of a block can differ by several times. For example, under the zero P/E cycle and 12-month retention time condition, the maximum  $N_{retry}$  value of tested blocks was 3× larger than the minimum  $N_{retry}$  value. The root cause of block-level  $N_{retry}$  variations is genetic process variability among blocks (e.g., different thickness of  $T_{OX}$  or flash cell size) resulting from the complex 3D NAND manufacturing procedure, as explained in Section 2.2.

Second, conventional P/E cycle-based block quality metrics are not adequate in predicting  $N_{retry}$  of the worst page in a block. That is, we cannot estimate  $N_{retry}$  of a block accurately using a block quality metric based on the P/E cycle and retention time. For example,  $N_{retry}$  values of blocks with the same P/E cycle (e.g., 3K P/E cycle) and the same retention time (e.g., 1-month retention time) are in the range between 8 and 16. If a  $N_{retry}$

Fig. 6. Block-level Nretry distributions.

predictor were based on the P/E cycle and retention time only, it would be impossible to estimate  $N_{retry}$  of a block accurately. Our key observations from Figure 6 strongly suggest that we need a *read-latency-centric new measure* for predicting  $N_{retry}$  of a block so that we can manage SSD read requests in a priority-aware fashion.

## 3.2 Cause 2: Priority-Oblivious Block Management

It is commonly accepted that in existing priority-aware FTLs, it is not necessary to distinguish the quality of different flash blocks because a wear-leveling mechanism in an SSD tends to maintain the quality of all the blocks at a similar level. Therefore, although these FTLs honor the I/O priority until an I/O request is issued to flash chips at the frontend of FTLs, they do not employ priority-aware block management techniques in key FTL backend management modules.

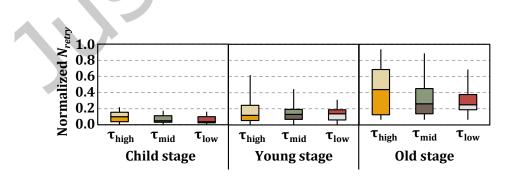

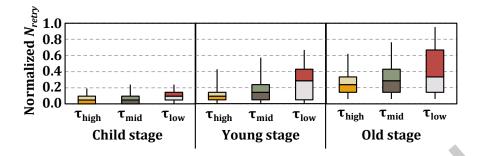

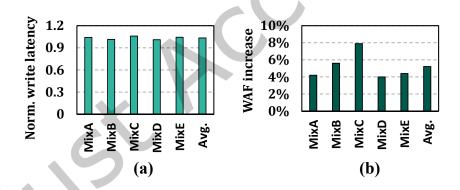

To validate the claim that block quality management is not necessary in an FTL because of a wear leveler, we evaluated if similar quality blocks are allocated to apps regardless of their app priority. We extended our simulation environment [11] so that it can accurately reflect the real device characterization results from our characterization study (in Section 4.2).<sup>2</sup> We collected  $N_{retry}$  values of target blocks of read requests for three apps used in Figure 1 at three distinct SSD lifetime stages: a child stage (at 500 P/E cycles), a young stage (at 1K P/E cycles), and an old stage (at 3K P/E cycles). For this evaluation, We used three traces were collected from running Yahoo! Cloud Service Benchmark [29] using RocksDB [30] with three different access patterns: an update-heavy workload (KV<sub>A</sub>), a read-intensive workload (KV<sub>B</sub>), and a read-modify-write workload (KV<sub>F</sub>). A high-priority app,  $\tau_{high}$ , executes KV<sub>B</sub> while two lower-priority apps,  $\tau_{mid}$  and  $\tau_{low}$ , run KV<sub>F</sub> and KV<sub>A</sub>, respectively.

Figure 7 shows block-level  $N_{retry}$  distributions of each app using box plots. In Figure 7, block-level  $N_{retry}$  values are normalized  $N_{retry}$  values between 0 and 1, where the lower value, the lower  $N_{retry}$  value. Unlike the common belief on the homogeneous quality because of an effective wear leveler of an FTL, the box plots of Figure 7 indicate that flash blocks with heterogeneous block quality were randomly allocated to three apps. For example, in all three SSDs,  $\tau_{low}$  was allocated to better blocks than  $\tau_{high}$ . Furthermore, at the old stage of the SSD lifetime, most poor blocks were allocated to  $\tau_{high}$ . This observation strongly suggests that the block quality of flash blocks is not similarly maintained, thus requiring priority-aware block quality management for effective read-performance differentiation.

## 3.3 Cause 3: No Read-Over-Read Preemption

Existing command preemption techniques focus on suspending slow ongoing commands such as program and erase operations when a new read command is issued because their latency is  $5.7 \times$  and  $30.4 \times$  longer than that

<sup>2</sup>See Section 6.1 for a detailed description of our simulation environment.

Fig. 7. Per-app block-level Nretry variations.

of a read, respectively [31, 32]. When a read command conflicts with another ongoing read command, the new read command must wait until the ongoing read command is completed although it is a higher-priority read command.

When there is little difference in read latency among different blocks (as incorrectly assumed in existing priority-aware FTLs), there may not be a strong need for supporting read-over-read preemption because an extra latency delay for a high-priority app may not be significant unless a large number of low-priority reads were intensively issued to the same target flash chip before the high-priority read. However, when an FTL supports read-latency-aware block management over priorities, a read-over-read preemption mechanism makes a big difference for high-priority reads, especially for their tail latency. In such an FTL, since the read latency of high-quality blocks would be shorter than that of low-quality blocks unless the read-over-read preemption is efficiently supported, the read latency of high-priority reads can be substantially degraded by low-priority reads.

To understand the impact of read-over-read preemption on the read tail latency when read-latency-aware block management is fully supported, we compared the read-latency distributions of three apps used in Figure 7,  $\tau_{high}$ ,  $\tau_{mid}$ , and  $\tau_{low}$ , under two FTL configurations, one with a read-over-read preemption mechanism, rorFTL, and the other without it, nopFTL. Both FTLs were configured to guarantee that a higher-priority app is allocated to blocks with shorter read latency. The 99-percentile tail latency of  $\tau_{high}$  under nopFTL was up to 37.4% longer than that under rorFTL in the old SSD. Furthermore, the average read latency of  $\tau_{high}$  was up to 25% longer than that under rorFTL as well.

## 4 Read-Latency-Centric Block Marker

To keep track of the heterogeneous block quality in terms of the read latency, we build a new block quality model that can accurately estimate tREAD of a block. Unlike many existing block quality markers [21, 33, 34] which focus on predicting the wear status of a block, ReadGuard needs a block quality marker that can be used to estimate tREAD of a block. Since  $N_{retry}$  is the only run-time variable in deciding tREAD, the proposed block quality model, the  $N_{retry}$  predictor nr(B) of a block B, aims to predict the  $N_{retry}$  value of the slowest page in a block B. To the best of our knowledge, the proposed nr(B) model is the first block quality metric that is specialized for estimating  $N_{retry}$ .

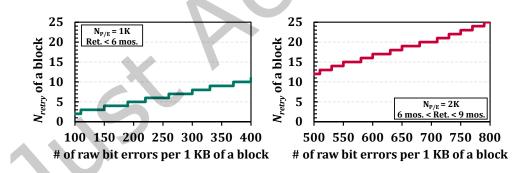

In developing an effective nr(B) model, we explore a strong correlation between  $N_{retry}$  of a block *B* and the raw bit error rate (RBER) of the block *B*.<sup>3</sup> In order to understand the relationship between  $N_{retry}$  and RBER of a block, we conducted a characterization study using real 3D TLC NAND flash chips. (See Section 4.2 for a detailed description of our methodology.) Figure 8 illustrates how  $N_{retry}$  and RBER of a block are related to each other in different P/E cycles and retention months. As shown in Figure 8,  $N_{retry}$  of a block can be expressed as a step function of RBER of a block. Therefore, we take a two-step approach to building a nr(B) model. As a first step, we predict the number of raw bit errors of the block *B*. Based on the estimated number of raw bit errors, we predict the  $N_{retry}$  of the block *B*.

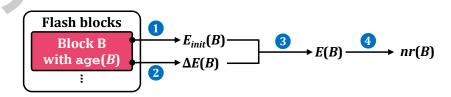

As explained in Section 2.2, raw bit errors of a block consist of two major error sources: the bit errors caused by *program disturb* and *retention loss*, respectively. The bit errors by program disturb occur when pages in a block are programmed, while the bit errors by retention loss continually increase after the pages in the block are written. Therefore, it is logical to build a nr(B) model using two submodels that correspond to two error sources of a block. Figure 9 conceptually illustrates how nr(B) of a block *B* is decided under the proposed method. When nr(B) of the block *B* is needed at time  $t_{cur}$ , two error attributes of the block *B*,  $E_{init}(B)$  and  $\Delta E(B)$ , are computed. The  $E_{init}(B)$  attribute (**1**) represents the number of *initial* raw bit errors of the block *B* when its pages were most recently written at time  $t_s$  (where  $t_s \leq t_{cur}$ ). The  $E_{init}(B)$  attribute indicates how much the block *B* was affected by program disturbance. The  $\Delta E(B)$  attribute (**2**) is used to estimate the number of errors that have been

<sup>&</sup>lt;sup>3</sup>Similar to the definition of  $N_{retry}$  of a block, we define the RBER value of a block as the RBER value of the worst page in a block.

accumulated to the block *B* since it was programmed at time  $t_s$ . The  $\Delta E(B)$  attribute represents how much the block *B* was affected by retention loss during the time interval  $(t_s, t_{cur}]$ . By adding  $E_{init}(B)$  and  $\Delta E(B)$  values, the total number E(B) of raw bit errors of the block *B* at time  $t_{cur}$  is computed (③). Finally, nr(B) is computed using a step function that relates E(B) to nr(B) (④). Note that in Figure 9, the block *B* has an additional attribute age(B). The age(B) attribute, which represents the wear status of the block *B*, plays a key role in computing both  $E_{init}(B)$  and  $\Delta E(B)$  are significantly affected by the wear status of the block *B*.

# 4.1 NAND Age Predictor: age(B)

The key prerequisite of estimating the number of raw bit errors of a block *B* is to know the accurate flash wear status of the block because the number of raw bit errors of the block varies significantly depending on the wear status of flash cells in the block [19, 21, 22]. For example, the number of retention error bits of a block under the same retention time condition (e.g., 12 months) can be several times different due to the varying wear status of the blocks. As discussed in Section 2.2, the flash wear status is closely related to the state of tunnel oxide in flash cells (i.e., a trap density). However, it is practically impossible to measure the trap density during run-time. As an alternative metric to differentiate the wear status of a flash block, several previous studies [21, 33, 34] have exploited the number N(t) of retention bit errors *after* the *t*-month retention time at 30°C.<sup>4</sup> In our study, following the common industry practice (i.e., the JEDEC standard [38, 39]), we use N(12) with the 12-month retention time.<sup>5</sup>

Although N(12) is an accurate indicator of the flash wear status of a block, it is still not a practical metric to be used during run time because it measures *future bit errors* after 12 months since the block was programmed.

<sup>5</sup>Although different retention times (e.g., six months) may be effective as well, we use the 12-month retention time requirement in this paper because it is commonly used as the worst-case reliability condition in practice.

Fig. 8. A relationship between RBER and Nretry values of flash blocks under different operating conditions.

Fig. 9. An overview of predicting  $N_{retry}$  of a block *B*.

<sup>&</sup>lt;sup>4</sup>Previous studies about NAND physics have shown that the number of retention bit errors has a near-linear relationship with the number of traps [35–37]. Furthermore, for recent multi-level flash memory, retention errors are responsible for the majority of the total number of raw bit errors, especially when the flash memory gets aged [19, 22, 24].

ACM Trans. Storage

ReadGuard: Integrated SSD Management for Priority-Aware Read Performance Differentiation • 11

| Variable           | Description                                                                    |

|--------------------|--------------------------------------------------------------------------------|

| $N_{P/E}$          | P/E cycles                                                                     |

| tERASE             | Erase latency                                                                  |

| $E_0$              | No. of bit errors of an LSB page in the first WL right after program           |

| L <sub>dwell</sub> | Average length of time interval between successive erase (effectively at 30°C) |

Table 1. A summary of variables for the age(*B*) attribute.

Because of this reason, N(12) is mostly used *as an off-line metric* for characterizing the wear status of flash cells. Therefore, we need an accurate *online* predictor for N(12). Note that the most common index for the flash wear status, the number  $N_{P/E}$  of program and erase cycles, does not accurately predict N(12) because it cannot account for key variations that affect the flash wear status such as process variability, I/O workload variations, and operating environment variations [21].

In order to design an accurate online predictor for N(12), we use RealWear [21], which is one of the most accurate flash aging metrics. Our proposed N(12) predictor of a block B, denoted as age(B), uses four run-time accessible parameters that are summarized in Table 1. In addition to  $N_{P/E}$ , three additional parameters are used: the erase latency *tERASE*, the number  $E_0$  of bit errors of an LSB page in the first wordline, and the average length  $L_{dwell}$  of time intervals between successive erase operations at 30°C.<sup>6</sup> The additional three parameters are used to complement the weaknesses of  $N_{P/E}$  as a wear status predictor. For convenience, age(B) is a normalized value by computing a ratio of N(12) of the block B to the maximum number of bit errors that can be corrected by an ECC module. When the block B is *alive* (i.e., it can reliably store data under the 12-month retention requirement),  $0 \le age(B) \le 1$ . From the proposed predictor equation in [21], age(B) can be expressed as:

$$age(B) = c_0 + c_1 \cdot N_{P/E} + c_2 \cdot tERASE + c_3 \cdot E_0 + c_4 \cdot ln(L_{dwell}).$$

Five coefficients,  $c_0$ ,  $c_1$ ,  $c_2$ ,  $c_3$ , and  $c_4$ , were estimated by the least-squares approximation method. The constant term  $c_0$  reflects inborn defects from a manufacturing process. (See the reference [21] for a complete description of RealWear including its validation results as a NAND age predictor.)

# 4.2 N<sub>retry</sub> Predictor Function: nr(B)

**Model Construction.** As described in Figure 9, the total number E(B) of raw bit errors of a block *B* at time  $t_{cur}$  is calculated by a sum of  $E_{init}(B)$  and  $\Delta E(B)$  at time  $t_{cur}$ . The  $E_{init}(B)$  value of the block *B*, which indicates how much flash cells were affected by program disturb after the block *B* was programmed, is known to have a strong and positive linear correlation with the wear status of flash cells [21]. Therefore,  $E_{init}(B)$  can be expressed as:

$$E_{init}(B) = c_5 \cdot \text{age}(B) + c_6. \tag{1}$$

In Equation (1), the first term represents the number of raw bit errors of a block induced by the program disturbance effect and the second term represents the number of inborn bit errors of a block from a manufacturing process.<sup>7</sup> In order to find  $E_{init}(B)$  at time  $t_{cur}$ , we use the  $E_{init}(B)$  value at time  $t_s$ , the time when the block was most recently programmed. Since age(B) changes only when the block is erased,  $E_{init}(B)$  at time  $t_s$  is still valid at time  $t_{cur}$  because the block *B* was erased most recently at time  $t_s$ .

<sup>&</sup>lt;sup>6</sup>The impact of  $L_{dwell}$ , which models the effect of I/O workload variations and operating environment variations on the flash wear status, significantly varies depending on the operating temperature. For example,  $L_{dwell}$  of 1 hour at 50°C has the same impact as  $L_{dwell}$  of 13 hours at 30°C. We used the baseline temperature of 30°C in  $L_{dwell}$ . When  $L_{dwell}$  at T°C was measured, it is converted to  $L_{dwell}$  at 30°C using the Arrhenius's Law [21, 22].

<sup>&</sup>lt;sup>7</sup>To decide  $c_5$  and  $c_6$ , we used the non-linear least squares algorithm to fit  $E_{init}(B)$  to the measurement data from a characterization study.

The  $\Delta E(B)$  value of the block *B* at time  $t_{cur}$  indicates how many additional raw bit errors were accumulated to the block *B* since it was most recently programmed at time  $t_s$ . As retention loss and read disturbance account for most of the additional raw bit errors, the proposed function employs two variables to reflect these error sources: the data retention time  $T_{ret}$  and the number  $N_{read}$  of read operations to a block. As well known, the additional raw bit errors by retention loss have a logarithmic relationship with  $T_{ret}$  [19, 24, 25, 40], while the additional raw bit errors by read disturbance phenomenon are exponentially increased with  $N_{read}$  [41, 42].<sup>8</sup> Since the flash wear status (e.g., age(B)) of a block significantly affects the additional raw bit errors by each error source, our proposed  $\Delta E(B)$  can be expressed as follows:

$$\Delta E(B) = c_7 \cdot (\text{age}(B) + c_8) \left\{ ln \left( 1 + T_{ret} \right) + e^{(c_9 \cdot N_{read})} \right\}.$$

(2)

To derive five coefficients,  $c_5$ ,  $c_6$ ,  $c_7$ ,  $c_8$ , and  $c_9$ , we used the non-linear least squares algorithm by fitting measurement data from our device characterization study to Equation (2).<sup>9</sup> The parameters  $c_0$  to  $c_9$  are fitting coefficients and constants to fine-tune the final polynomial equation to reflect the error characteristics of target chips, which can be determined via real-device characterization of the chips. In Equation (2),  $T_{ret}$  is the equivalent data retention time at 30°C. The specific thermal condition of 30°C in  $T_{ret}$  is needed because the impact of the retention time on the number of retention errors varies significantly depending on the data retention temperature. For convenience, we convert a data retention time  $T_{ret}^{x^{\circ}C}$  at x°C to a data retention time  $T_{ret}$  at 30°C using the Arrhenius's Law [21, 22]. In order to find  $\Delta E(B)$  at time  $t_{cur}$ , we use age(B) at time  $t_s$  and  $(t_{cur} - t_s)$  at 30°C. To find  $(t_{cur} - t_s)$  at 30°C, we read the current temperature from a thermal sensor in an SSD which is commonly adopted for internal management of an SSD such as performance throttling for thermal management [43].

Based on  $E_{init}(B)$  and  $\Delta E(B)$  at time  $t_{cur}$ , the total number E(B) of error bits at time  $t_{cur}$  is computed by adding  $E_{init}(B)$  and  $\Delta E(B)$  at time  $t_{cur}$ . Based on E(B),  $N_{retry}$  of the block *B* can be predicted by using a step function S() as shown in Figure 8. The proposed  $N_{retry}$  predictor nr(B), therefore, can be summarized as:

$$nr(B) = S(E_s(B) + \Delta E(B)).$$

<sup>(3)</sup>

**Validation Methodology.** To evaluate our proposed nr(B), we performed comprehensive evaluations using 160 real 3D flash chips.<sup>10</sup> To avoid sample distortions, we divided our test samples into three groups: 60 chips for model construction, 60 chips for validating the adequacy of our model, and the other 40 chips for building a simulation environment (as will be explained in Section 6.1). In our evaluations, we carefully designed each measurement session following the test procedures of the JEDEC industry standards [38, 39, 46] for commercial SSDs. These standards specify the test methodology (e.g., a sample size or test conditions) and qualification criteria for evaluating NAND flash memory. One key recommendation for high-confidence characterization studies is to use more than 39 flash chips from 3 different wafers. Since we have used 60 flash chips from 5 wafers for designing the model, we believe that our sample size is sufficient to obtain statistically meaningful results. For model validations, we used another group of 60 chips. From each chip, to minimize potential distortion in our results, we evenly selected 16 blocks from different physical locations of the chip and tested all the pages in

<sup>&</sup>lt;sup>8</sup>The retention errors shift program states to the left while the read disturbance errors shift erase state to the right. Therefore, these two error sources affect the number of bit errors independently.

<sup>&</sup>lt;sup>9</sup>The next page describes the validation methodology in detail, including how we measured the RBER values of the tested blocks.

<sup>&</sup>lt;sup>10</sup>In our characterization study, we used 48-layer 3D TLC flash chips from the same NAND flash manufacturer. Even though we were able to validate our new error model only for the specific type of chip (due to the limited access to real chips in academia), we strongly believe that our model (and the methodology to derive the model) can be used for a wide range of chips due to two reasons. First, our tested chips well represent modern 3D NAND flash memory because most commodity chips including SMArT/TCAT/BiCS [44, 45] have similar structures and cell types, e.g., vertical channel structures, gate-all-around transistors, and charge-trap type flash cells, thereby sharing key device characteristics. Second, we derive our model based on well-known error characteristics of NAND flash memory that are validated in a large body of prior work (using different types of chips) [19, 22], without relying on device-specific or technology-specific characteristics.

each block. To evaluate the impact of different variable combinations, we created test block samples for each combination by precisely controlling four variables of age(B) and  $T_{ret}$ . For example, to evaluate the impact of combinations of n  $L_{dwell}$  times and m  $T_{ret}$  times, we generated  $n \times m$  samples, and each sample consists of 960 blocks (16 blocks × 60 chips).

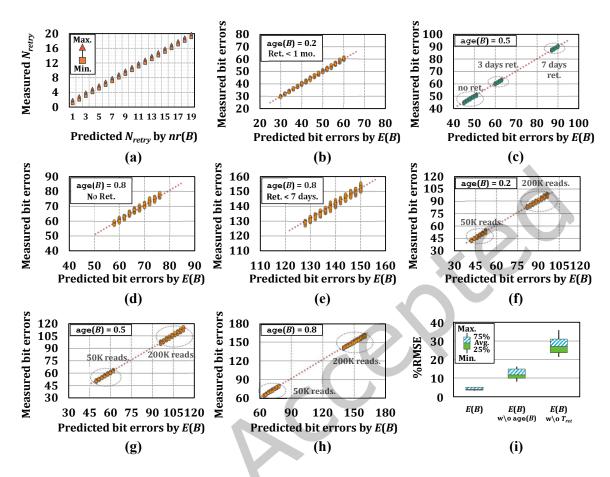

**Validation Results.** In order to demonstrate that nr(B) is an accurate predictor that predicts  $N_{retry}$  of a flash block, we present four key validation results. Figure 10(a) shows how well nr(B) predicts  $N_{retry}$  of a flash block. The x-axis of the figure represents the predicted  $N_{retry}$  values nr(B), while the y-axis shows a distribution of measured  $N_{retry}$  values from real flash blocks with the same nr(B) value using a box plot. For a given v as a predicted  $N_{retry}$  value, a min-max plot shows a distribution of measured  $N_{retry}$  values within an interval [min(v), max(v)] where min(v) is the minimum measured  $N_{retry}$  value and max(v) is the maximum measured  $N_{retry}$  value among the blocks with v as their  $N_{retry}$  predictor values. As shown in Figure 10(a), nr(B) works properly as an on-line  $N_{retry}$  predictor of a block. The predicted  $N_{retry}$  values were very close to the measured  $N_{retry}$  values from real flash blocks. Especially, for all min-max plots shown in Figure 10(a), the difference between min(k) and max(k) at most 1 for all  $k \ge 0$ . Thus, if  $nr(B_x) < nr(B_y)$ , it is guaranteed that  $N_{retry}$  of  $B_x \le N_{retry}$  of  $B_y$ . That is, nr(B) is sufficient to distinguish the difference in  $N_{retry}$  of flash blocks.

We also validated the E(B) model from Equation (2) with the measured data under seven different conditions. Figures 10(b), 10(c), and 10(d), (e) compare the predicted E(B) values with the measured ones when the data retention time was changed in young blocks (with age(B) = 0.2), moderately-worn blocks (with age(B) = 0.5), and old blocks (with age(B) = 0.8), respectively. Figures 10(f), 10(g), and 10(h) compare predicted E(B) values with measured ones when the number of experienced read operations of a block was changed in young blocks (with age(B) = 0.2), moderately-worn blocks (with age(B) = 0.5), and old blocks (with age(B) = 0.8), respectively. Note that the data retention time in Figures 10(b), 10(c), 10(d), and 10(e) assumes the retention temperature of 30°C, and the read operations in Figures 10(f), 10(g), and 10(h) are fully sequential pattern. In all cases, the percentage root mean square error (%RMSE) is less than 10%, which means that E(B) can accurately predict bit errors of the block *B* under various conditions (various  $N_{P/E}$ ,  $T_{ret}$ , and  $N_{read}$ ).

To demonstrate that our E(B) model is a simple model to implement in practice with required high accuracy, we evaluated if the current E(B) model includes redundant model variables. We evaluated the prediction accuracy of simpler E(B) models with smaller model variables. Figure 10(d) compares %RMSE values of two simpler E(B) models with the proposed E(B) model based on the difference between predicted E(B) values and the measured E(B) values in each model. We considered two simpler models, C1 and C2, with three model variables only: (C1) the normalized  $N_{P/E}$  value was used instead of age(B) value in Equation (1), and (C2)  $T_{ret}$  was not included in Equation (2). As shown in Figure 10(d), both simpler models exhibit much lower prediction accuracy over the proposed E(B) model, thus demonstrating that the proposed E(B) model has no redundant model variable.

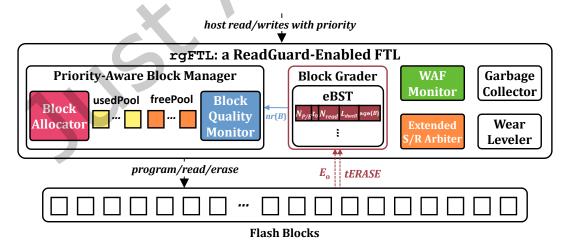

# 5 Design of ReadGuard

The key contribution of the new block quality marker described in Section 4 is that it enables an FTL to manage its blocks based on the read latency level of each block. In this section, we describe ReadGuard, an integrated priority-aware flash management scheme based on our new block quality marker. A key design requirement of ReadGuard is to support the read performance differentiation in proportion to the app priority without affecting the performance/lifetime of a ReadGuard-enabled SSD. Figure 11 shows an overall organization of an FTL, called rgFTL, that employs the proposed ReadGuard scheme.

It is challenging for an FTL to determine whether an I/O request is latency-sensitive or not based on the limited information. As a more practical and straightforward solution, we assume that an app determines its own I/O priority based on a better understanding of I/O responsiveness. For passing I/O priority information from apps to the FTL via the kernel I/O stack, we modify the Linux kernel's process control block to keep the I/O priority

Fig. 10. Block quality function validation results.

value and employ NVMe's queueing-based I/O priority feature. During the initialization phase, an app sets its I/O priority value using a custom API. When an app issues an I/O request, the modified kernel I/O stack (block layer and NVMe driver) retrieves the app's I/O priority value from the process control block and inserts the I/O request into the appropriate NVMe queue based on the app's priority value. The host interface layer in the FTL then prioritizes the I/O request based on the priority level of the NVMe queue from which it comes.

As shown in Figure 11, the proposed rgFTL, which is based on an existing page-level FTL, has three key modules for supporting ReadGuard: the block grader (BGR), the priority-aware block manager (PBM), the WAF monitor (WM), and the extended suspend/resume arbiter (ESRA). The BGR module keeps track of the block quality nr(B) of a block *B*. To this end, it manages an extended block status table (eBST) that stores parameters that are related to the block quality function. The PBM module is in charge of matching apps' priority with the quality of allocated blocks. To manage free blocks and used blocks based on their nr(B) values, the PBM module uses freePool and usedPool (which work as a typical priority queue). The block allocator (BA) of the PBM module ensures that higher-priority apps use higher quality blocks over lower-priority apps at the initial block allocation time. The block quality monitor (BQM) of the PBM module monitors if there is block-quality inversion among allocated blocks for apps with different priorities. When there is block-quality inversion, the BQM module

resolves it by migrating data from quality-inverted blocks. The ESRA module preempts an ongoing operation when the operation conflicts with an incoming read request on the same flash chip.

In order for rgFTL to control the amount of additional writes by the BQM module (so that it cannot negatively affect the SSD lifetime), rgFTL dynamically changes the condition of block-quality inversion depending on the accumulated amount of writes by the BQM module. The WM module monitors the amount of extra writes from the BQM module and computes its proportion in the total amount of writes for SSD-internal management tasks (e.g., a garbage collector and a wear leveler). When the extra writes from the BQM module exceed the current upper bound, the WM module changes the condition of block-quality inversion to be more strict. If the extra writes from the BQM module are smaller than the current upper bound, the WM module modifies the condition of block-quality inversion to be easier to meet. (See Section 5.3.)

## 5.1 Block Grader

Algorithm 1 shows how the BGR module grades blocks by exploiting the proposed block-quality model in Section 4. To accurately estimate nr(B) of a block B, the BGR module needs the following five values, the number  $N_{P/E}$  of program/erase cycles, the data retention time  $T_{ret}$ , the number of reads  $N_{read}$ , the average length  $L_{dwell}$ of time intervals between successive erase operation, the erase latency tERASE, and the number  $E_0$  of bit errors immediately after program<sup>11</sup>, for each block.  $N_{P/E}$  is simple to manage because it increments by one whenever the block B is erased. At time t,  $T_{ret}$  of the block B is estimated by  $(t - t_0)$  where  $t_0$  is the time when the block Bwas most recently programmed with its first page. The BGR module resets  $t_0$  for each block B after the block Bis erased. The BGR module modifies  $L_{dwell}$  whenever a block is erased using  $T_{ret}$  and the current temperature from a thermal sensor. Since the remaining two parameters, tERASE and  $E_0$ , that are related to age(B) attribute, change slowly over the number of block erasures, the BGR module tracks these values at a coarse granularity, say every 100 P/E cycles. tERASE is directly measured at the flash controller, and  $E_0$  is measured by reading back the first page of a block immediately after the first page is programmed to the block. Once new tERASE and  $E_0$  are measured for a block, the BGR module updates the age(B) value for the block in the eBST. When nr(B) value is

<sup>11</sup>Our metric uses  $E_0$  of an LSB page in the first wordline among a block.

Fig. 11. An overview of the proposed rgFTL.

needed by rgFTL at time *s* for the block *B*, the BGR module returns nr(B) using the current age(*B*) in the eBST, (*s* - *t*<sub>0</sub>), and *N*<sub>read</sub>.

In summary, the BGR module maintains five per-block parameters in the eBST,  $N_{P/E}$ ,  $t_0$ ,  $N_{read}$ ,  $L_{dwell}$ , and age(*B*). However, its storage overhead is negligible because these parameters are managed at the block granularity. For example, four bytes would be sufficient to store each of the four parameters, so the extra memory of 5 MB would be sufficient for a 2 TB SSD (see Section 6.1). Although it also takes a few cycles to update parameters for every flash erase operation, the extra cycles would be negligible because the latency of erase operations is several orders of magnitude longer than the extra cycles.

Algorithm 1 Block grading 1: Initialize parameters for each block in eBST:  $N_{P/E}$  (Number of program/erase cycles)  $t_0$  (Last programming time of block) N<sub>read</sub> (Number of reads)  $L_{dwell}$  (Average time interval between erase operations) age(B)2: **function** UPDATEERASERELATEDPARAMETERS(block *B*, time *t*) Initialize two variables: *tERASE* and  $E_0$ 3: Increment  $N_{P/E}$  by 1 4: Update  $T_{ret}$  for B as  $(t - t_0)$ 5: 6: Reset  $t_0$  for *B* after each erase operation Modify  $L_{dwell}$  based on  $T_{ret}$  and current temperature 7: if  $N_{P/E}$  modulo 100 is 0 then 8: Measure *tERASE* directly from the flash controller 9: Measure  $E_0$  by reading the first page of *B* after programming 10: Update age(B) for B 11: 12: end if Free two variables: tERASE and  $E_0$ 13: 14: end function 15: **function** UPDATEREADRELATEDPARAMETER(block B) Increment  $N_{read}$  by 1 16: 17: end function 18: **function** CALCULATEBLOCKQUALITY(block *B*, time *s*) **return** Block quality nr(B) for B using age(B) in eBST,  $(s - t_0)$ ,  $N_{read}$ 19: 20: end function 21: Main: When block *B* needs to be erased to serve a write request: Call updateEraseRelatedParameters(B, t) When a read request arrives to block B: Call updateReadRelatedParameter(B) When block quality *nr*(*B*) for block *B* is needed at time *s*: Call CALCULATEBLOCKQUALITY(B, s)

| Algorithm 2 Priority-Aware block management with three priorities                                               |

|-----------------------------------------------------------------------------------------------------------------|

| 1: Initialize:                                                                                                  |

| <pre>freePool, usedPool (priority queues ordered by nr(B))</pre>                                                |

| subP <sub>high</sub> , subP <sub>mid</sub> , subP <sub>low</sub> (subpools in freePool for each priority level) |

| $\mu_{high}, \mu_{mid}$ (per-priority inversion margins)                                                        |

| $GC_{thr}$ (GC threshold)                                                                                       |

| 2: function AllocateBlock(app $\tau_i$ , priority $p_i$ )                                                       |

| 3: Allocate block <i>B</i> from $subP_i$                                                                        |

| 4: Delete block <i>B</i> in subP <sub>i</sub>                                                                   |

| 5: Insert block B to usedPool                                                                                   |

| 6: <b>if</b> Number of free blocks in $subP_i \leq GC_{thr}$ then                                               |

| 7: Invoke garbage collection for $subP_i$                                                                       |

| 8: end if                                                                                                       |

| 9: Update subP <sub>i</sub> pointers                                                                            |

| 10: end function                                                                                                |

| 11: <b>function</b> DetectInversion(priority $p_i$ , priority $p_j$ )                                           |

| 12: Initilize allInversionIsResolved to FALSE                                                                   |

| // Detect all possible block-quality inversion                                                                  |

| 13: while allInversionIsResolved is <i>FALSE</i> do                                                             |

| 14: Find the worst block $B_w$ of $\tau_i$ and the best block $B_b$ of $\tau_j$                                 |

| 15: <b>if</b> $nr(B_w) - nr(B_b) > \mu_i$ <b>then</b> Call ResolveInversion $(B_w, B_b)$                        |

| 16: else                                                                                                        |

| 17: Set allInversionIsResolved to <i>TRUE</i>                                                                   |

| 18: end if                                                                                                      |

| 19: end while                                                                                                   |

| 20: end function                                                                                                |

| 21: <b>function</b> resolveInversion(block $B_{low}$ , block $B_{high}$ )                                       |

| // $B_{low}$ is a lower-quality block and $B_{high}$ is a higher-quality block                                  |

| 22: <b>if</b> $age(B_{high}) < age(B_{low})$ <b>then</b>                                                        |

| 23: Migrate valid data of $B_{high}$ to a new block in low-priority free pool subP <sub>low</sub>               |

| 24: Move $B_{high}$ to high-priority free pool subP <sub>high</sub>                                             |

| 25: else                                                                                                        |

| 26: Refresh valid data of $B_{low}$ to a new block                                                              |

| // $T_{ret}$ and $N_{read}$ are reset to 0                                                                      |

| 27: end if                                                                                                      |

| 28: end function                                                                                                |

| 29: Main:                                                                                                       |

| When a $\tau_i$ with $p_i$ requires a free block:                                                               |

| Call AllocateBlock $(\tau_i, p_i)$                                                                              |

| Every predefined interval:                                                                                      |

| Call detectInversion( $p_{high}, p_{mid}$ )                                                                     |

| Call detectInversion( $p_{high}, p_{low}$ )                                                                     |

| Call detectInversion( $p_{mid}, p_{low}$ )                                                                      |

## 5.2 Priority-Aware Block Manager

The main role of the PBM module, which is the core component of ReadGuard, is to guarantee that blocks are managed so that the priority order of apps is ensured. Algorithm 2 shows how the PBM module manages blocks based on I/O priorities of apps. The PBM module maintains two ordered queues, freePool and usedPool, of free blocks and used blocks, respectively. Both freePool and usedPool are ordered by nr(B) values. When the BA module of the PBM module allocates a free block to an app  $\tau_i$  with priority  $p_i$ , it first searches for a proper free block (from freePool) that meets the priority order with the other apps. To make the search process more efficient, when N different priority levels are supported, blocks in the freePool are grouped into N subpools, subP<sub>0</sub>, ..., subP<sub>N-1</sub>, where blocks in subP<sub>i</sub> have higher quality over ones in subP<sub>j</sub> if i < j. When  $\tau_i$  with  $p_i$  needs a free block (that were sorted by their nr(B) values), the BA module maintains one pointer for each subpool that points to the starting location of each subpool within freePool. Whenever a block is consumed from a subpool or a new block is added to freePool, subpool pointers are updated.

Although the BA module honors the priority order of apps when a block is initially assigned to a requesting app, it cannot completely prevent block-quality inversion because the quality of the allocated block dynamically changes. The BQM module is responsible for detecting block-quality inversion of blocks in usedPool during run time. In order to manage the number of extra writes for resolving block-quality inversions, we introduce two additional variables in deciding if block-quality inversion occurs between blocks. Per-priority inversion margins,  $\mu_{high}$  and  $\mu_{mid}$ , are used in deciding block-quality inversion in  $\tau_{high}$  and  $\tau_{mid}$ , respectively. In  $\tau_{high}$ , when  $nr(B_w)$  of the worst block  $B_w$  of  $\tau_{high}$  is larger than  $nr(B_b)$  of the best block  $B_b$  of  $\tau_{mid}$  at least by  $\mu_{high}$ , there exists block-quality inversion between  $\tau_{high}$  and  $\tau_{mid}$ . Similarly, in  $\tau_{mid}$ , when  $nr(B_w)$  of the worst block  $B_b$  of the best block  $B_w$  of  $\tau_{nid}$  is larger than  $nr(B_b)$  of the best block is strongly dependent on two per-priority inversion margins. When the margins are set to a small value (e.g., 1), more block pairs may satisfy the condition of block-quality inversion. On the other hand, when the margins are set to a large value (e.g., 10), fewer block pairs can meet the condition. By dynamically adjusting  $\mu_{high}$  and  $\mu_{mid}$ , we control the number of quality-inverted blocks, thus managing the amount of extra writes needed for resolving quality-inverted blocks within an acceptable limit.

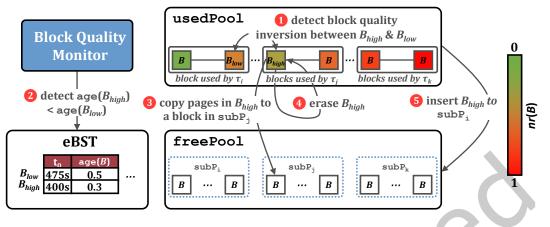

To find block-quality inversion, every predefined interval<sup>12</sup>, the BQM module checks if the difference of nr(B) values between the worst used block for  $\tau_{high}$  and the best used block for  $\tau_{mid}$  exceeds  $\mu_{high}$ . Similarly, the same check is performed between  $\tau_{mid}$  and  $\tau_{low}$ . When the BQM module identifies two quality-inverted blocks,  $B_{high}$  and  $B_{low}$ , it resolves them by one of two methods, one based on age(*B*) and the other based on  $T_{ret}$  and  $N_{read}$ . We assume that  $B_{high}$  is a higher quality block allocated for a lower-priority app  $\tau_{low}$  and  $B_{low}$  is a lower quality block allocated for a higher-priority app  $\tau_{high}$ .

As the first method, we check if there is inversion in age(B) values of  $B_{high}$  and  $B_{low}$ . That is, we check if  $age(B_{high}) < age(B_{low})$ . This type of block-quality inversion is possible, for example, when a high-priority write-intensive app  $\tau_{high}$  and a low-priority write-once app  $\tau_{low}$  run together. If a block  $B_{high}$  were allocated to  $\tau_{low}$  a long time ago, its  $age(B_{high})$  value could be lower than that of a block that was recently allocated to  $\tau_{high}$ because  $\tau_{high}$  tends to quickly increase age(B) values of its allocated blocks because of their frequent P/E cycles. We resolve the first type of block inversion by moving  $B_{high}$  to a free pool subP<sub>high</sub> of a high-priority app  $\tau_{high}$ . Furthermore, since data in  $B_{high}$  are moved to a free block B' in a free pool subP<sub>low</sub> of a low-priority app  $\tau_{low}$ , nr(B') should be larger than  $nr(B_{high})$ , thus mitigating future block inversion between  $\tau_{high}$  and  $\tau_{low}$ .

<sup>&</sup>lt;sup>12</sup>Since  $N_{retry}$  of a block increases slowly by  $T_{ret}$ , we set default interval length by seven days at 30°C.

Fig. 12. An example of age(B) inversion handling.

Figure 12 illustrates how the BQM works when inversion in age(B) values occurs using a high-priority app  $\tau_i$  and a low-priority app  $\tau_j$ . The BQM module first detects block-quality inversion between  $B_{high}$  and  $B_{low}$  (1) and finds  $age(B_{high}) < age(B_{low})$  by referencing the eBST (2). When the BQM module detects inversion in age(B) values, the BQM module moves data of the block  $B_{high}$  to a free block in  $subP_j$  (3) in Figure 12) and erases the block  $B_{high}$  (4). After that, the BQM module forces the block  $B_{high}$  to be moved to  $subP_i$  so that it can be used for a higher-priority app in a future block allocation time (5).

If the first method cannot be applied,  $age(B_{high})$  should be greater than or equal to  $age(B_{low})$ . Therefore,  $T_{ret}$  of  $B_{low}$  should be much larger than that of  $B_{high}$  if  $B_{high}$  and  $B_{low}$  could meet the condition of quality-inverting blocks. We resolve the second type of block inversion by refreshing (i.e., rewriting to the same block) data in  $B_{low}$ . Since  $T_{ret}$  of  $B_{low}$  resets to zero, the block quality of  $B_{low}$  should be better than that of  $B_{high}$ . Note that to avoid two types of block-quality inversion during run time, it is inevitable to move data between the affected blocks, thus possibly degrading the SSD lifetime. To avoid the SSD lifetime from being degraded by too many data movements from the BQM module, we need an intelligent mechanism to control the amount of data movements from the BQM module.

## 5.3 WAF Monitor

The main role of the WM module is to periodically monitor the write overhead from the BQM module and to properly adjust two run-time margin variables,  $\mu_{high}$  and  $\mu_{mid}$ , that are used in detecting quality-inverted blocks in  $\tau_{high}$  and  $\tau_{mid}$ , respectively. By modifying  $\mu_{high}$  and  $\mu_{mid}$  during run time, rgFTL can achieve high differentiation in read performance among apps with different priorities with little degradation on the SSD lifetime. Each margin variable is represented as a normalized number between 0 and 1 over the maximum observed  $N_{retry}$  value. In the current version of rgFTL, we allow the write overhead of the BQM module to be less than 10% of the total SSD-internal writes that are required for managing an SSD.<sup>13</sup>

In adjusting  $\mu_{high}$  and  $\mu_{mid}$ , the WM module considers the proportion p of additional writes by the BQM module over the total amount of writes for managing an SSD. The initial values of both margins are set to 0.1 so that the BQM module equally differentiates the read performance among three priorities. The WM module checks

$<sup>^{13}</sup>$ Although rather arbitrary, 10% was selected based on our observations from device characterization study. For all the tested flash blocks from 110 flash chips, they were still alive when their P/E cycles reached 110% of the maximum allowed P/E cycles.

the current p value at every monitoring interval.<sup>14</sup> When p is larger than 10%, the WM module increases the margin variables by 0.1 so that fewer blocks are detected as quality-inverting blocks, thus decreasing the write overhead from the BQM module. On the other hand, when p is smaller than 10%, the WM module decreases the margin variables by 0.1 so that more blocks can be detected as quality-inverting blocks, thus better differentiating read performance among apps with different priorities.

## 5.4 Extended Suspend/Resume Arbiter

The ERSA module extends an existing read-over-program/erase preemption mechanism [26] to support readover-read preemption. Since the PBM module fully manages flash blocks in a priority-aware fashion in rgFTL, when a higher-priority read should wait for a lower-priority read to complete, the higher-priority read may suffer from an excessive delay because the lower-priority read is likely to be serviced by a block with the long read latency. A straightforward solution to this problem may be to immediately suspend the ongoing read command when a higher-priority read is issued. However, supporting an immediate read preemption mechanism is quite challenging because 1) a flash chip should be modified to support read suspend/resume commands, and 2) large hardware resources are required for saving the transient read-internal states when suspended and restoring the save states for resuming the suspended read.

In the ESRA module, we employ a lazy suspension mechanism when a high-priority read is issued while a low-priority read is ongoing. The low-priority read is allowed to complete the current read step. However, if the low-priority read requires a read retry step because of a failed read, the next read retry step is suspended, thus being preempted for the high-priority read.

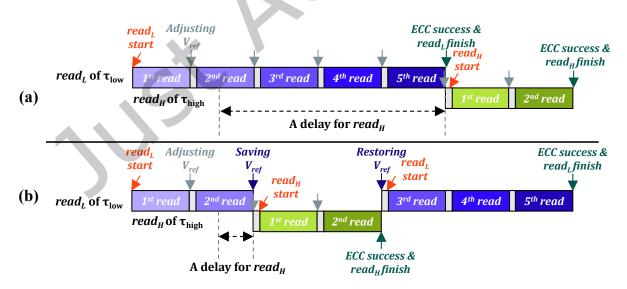

The current design of the ESRA module minimizes the amount of saved read-internal states when a read command is preempted because only  $V_{ref}$  of the last failed read step needs to be saved. Furthermore, a maximum delay of one read-retry step is acceptable for higher-priority reads because it causes a marginal increase in *tREAD*. Figure 13 illustrates how rgFTL handles two reads with different priorities with and without the ESRA module.

<sup>14</sup>To observe a steady WAF value, we defined a monitoring interval as the time it takes to perform a sufficient number (e.g., 5% of total blocks) of garbage collections (GC).

Fig. 13. An illustrative comparison of (a) rgFTL without the ESRA module and (b) rgFTL with the ESRA module.

As shown in Figure 13(a), without the ESRA module, a read command  $read_H$  of  $\tau_{high}$  must wait until the ongoing read command  $read_L$  of  $\tau_{low}$  that needs four steps  $V_{ref}$  adjustment (i.e.,  $N_{retry} = 4$ ) to complete. In contrast, as shown in Figure 13(b), the ESRA module waits until the ECC correction of the current  $read_L$  is complete. If the ECC fails, suspends  $read_L$  with its last used  $V_{ref}$  saved and issues  $read_H$  first. After  $read_H$  is completed with two read steps, the ESRA module restarts  $read_L$  with the stored  $V_{ref}$  where its read step was suspended. Since the FTL decides if read retries are needed (by checking if the ECC succeeds or fails), the ESRA module requires no change to NAND flash chips. It requires only tiny DRAM space to store  $V_{ref}$  values (two  $V_{ref}$  values for  $\tau_{high}$  and  $\tau_{mid}$ , respectively, for supporting three priorities) of suspended read commands at the FTL level.

## 5.5 Other FTL Modifications

In rgFTL, a garbage collector and a wear leveler need to be modified because these modules indirectly affect how blocks are allocated to different apps. We design the garbage collector and the wear leveler in such a way that as a result of garbage collection and wear leveling, the number of block swap operations by the BQM module does not significantly increase.

Changes in Garbage Collector. The garbage collector of rgFTL is triggered based on the number of free blocks in each subpool instead of the number of total free blocks in a conventional FTL. Although there exists a large number of free blocks in freePool, when the number of free blocks in subP<sub>i</sub> is less than a threshold value<sup>15</sup>, the garbage collector is invoked in the background and reclaims free blocks from usedPool. Each reclaimed free block *B* is inserted to a proper subpool (not necessarily to subP<sub>i</sub>) according to its age(*B*). When *B* is not inserted to subP<sub>i</sub>, the BA module rearranges its subpools so that subP<sub>i</sub> gets a new free block. In order to avoid block-quality inversion during the garbage collection, when the garbage collector moves the valid pages of a selected victim block B<sub>v</sub> to a target block B<sub>t</sub>, B<sub>t</sub> should be in the same priority group as B<sub>v</sub>. That is, if B<sub>v</sub> was allocated to  $\tau_k$ , B<sub>t</sub> must also be allocated to  $\tau_k$  or must be from subP<sub>k</sub>.

**Changes in Wear Leveler.** A common heuristic used in a wear leveler is to move write-hot data to a more reliable block [47–49]. However, if the wear leveler migrates data in a priority-oblivious fashion, data migrations by the wear leveler can cause block-quality inversion. For example, consider two apps  $\tau_i$  and  $\tau_j$  where the priority of  $\tau_i$  is higher than that of  $\tau_j$ . If  $\tau_j$  is write-intensive, a wear leveler may be invoked so that write-hot data of  $\tau_j$  can be moved to a more reliable block  $B_d$  (i.e., with a smaller age(*B*)). If the destination block  $B_d$  belonged to a higher priority group (e.g., in subP<sub>i</sub>), the BQM module might trigger a block swap operation in the near future to prevent block-quality inversion from  $B_d$ . The block-quality inversion occurs because the block quality of  $B_d$ , which was allocated to a lower-priority app  $\tau_j$ , can be better than that of the lowest quality block of a higher-priority app  $\tau_i$ .

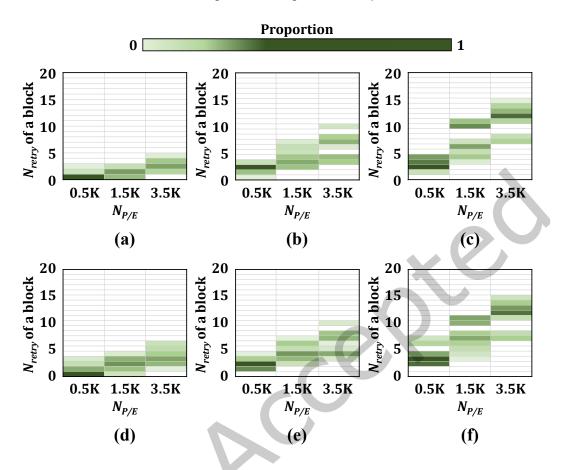

To avoid such successive block swap operations, the wear leveler of rgFTL employs an intra-priority mode as default. In the intra-priority mode, the wear leveler tries to minimize the difference in wear status of blocks that belong to the same priority group (i.e., used blocks for the same  $\tau_i$ ). Compared to a conventional wear leveler, the intra-priority mode alone may not be effective in leveling the wear status of the most-worn blocks when the data hotness is quite different depending on apps. For such rare cases, the wear leveler of rgFTL supports the inter-priority mode, which is invoked when the maximum difference in the wear status of all the blocks exceeds a threshold value. In the inter-priority mode, the wear leveler works in a conventional way, considering the wear difference of all the blocks, not the blocks only in the same priority group. Inevitably, the inter-priority mode will introduce additional block-quality inversion. However, if this inversion is quickly fixed by the BQM module, the wear leveler cannot reduce the maximum wear difference. Therefore, in the inter-priority mode, we tentatively

$<sup>^{15}</sup>$ We set the threshold value higher than the value that can maximize the internal parallelism of the SSD. That is, the modified garbage collector aims to maintain the number of free blocks in each subP as sufficient for composing a superblock.

disable the BQM module so that less reliable blocks can hold cold data longer, thus reducing the maximum wear difference among all the blocks.

## 6 Evaluation

## 6.1 Evaluation Methodology

**Simulation Setup.** To evaluate the effectiveness of rgFTL, we used an extended version of MQSim [11], a multi-queue SSD simulator with NVMe interface support. We extend MQSim in two directions to faithfully model a modern NAND flash-based SSD. First, we extended the NAND flash chip model of MQSim to simulate more realistic behavior of NAND flash blocks, based on real-device characterization of 40 3D TLC NAND flash chips. We modified the metadata structure of each simulated block to include multiple  $N_{retry}$  lookup tables that are indexed by a P/E-cycle interval and a data retention time. In the simulation setup stage, we randomly assigned a real characterization results of the real block. When simulating a read request to a page, the extended MQSim first queries the lookup tables with the current P/E cycle and retention time of the corresponding block and performs read retry operations  $N_{retry}$  times. Second, we modified the transaction scheduling unit of MQSim to support a read-over-read preemption mechanism as well as an existing read-over-program/erase preemption mechanism [26].

Table 2 summarizes the configurations of our evaluated SSD, which mimics a modern high-performance SSD. We configured the target SSD to have 2 TB capacity with eight channels, each of which has four 3D TLC flash chips. Each chip has four planes, and each plane consists of 1,888 blocks. Each block comprises 576 16 KB pages. We set flash operation timing parameters for *tREAD* (without read retry), *tPROG*, and *tERASE* to 45  $\mu$ s, 400  $\mu$ s, and 3.5 ms, respectively. We set the host interface to support a maximum bandwidth of 8.0 GB/s as specified by the PCI Express (PCIe) 4.0 standard [50]. A flash channel's I/O bandwidth can support 1.6 GB/s peak bandwidth, which is sufficient to support the host interface's peak bandwidth of eight channels.